# Measuring voltage converters

L-502-P-G-D-I L-502-P-G L-502-X-G L-502-X-G L-502-X-G-D L-502-X-X L-502-X-X

User manual

Revision 1.1.0 October 2017

http://en.lcard.ru en@lcard.ru

DAQ SYSTEMS DESIGN, MANUFACTURING & DISTRIBUTION

#### Author of the manual

Garmanov A.V.

## L-Card LLC

117105, Moscow, Varshavskoye shosse, 5, block 4, bld. 2 tel.: (495) 785-95-19 fax: (495) 785-95-14

### **Internet contacts**

http://en.lcard.ru

### E-Mail:

Sales department: en@lcard.ru

Technical support: en@lcard.ru

L-502 Module © Copyright 2006-2017, L-Card LLC. All rights reserved.

| Date    | Document<br>revision | Contents of the change                                                                                                                                                                                                                                                   |

|---------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06.2012 | 1.0.1                | Preliminary data                                                                                                                                                                                                                                                         |

| 07.2012 | 1.0.2                | Preliminary data                                                                                                                                                                                                                                                         |

| 11.2012 | 1.0.3                | The information on connection L-502 is added, as well as Chapter 6 an item 4.2.3.1, item 4.2.4.1, item 4.2.5, item 4.3, item is added by 4.4.                                                                                                                            |

| 01.2014 | 1.0.4                | Edited table 4-1, supplemented paragraphs. 1.3, 2.4, 2.5. 4.2.4                                                                                                                                                                                                          |

| 05.2014 | 1.0.5                | A comment is added to the item 5.1.2, page 51                                                                                                                                                                                                                            |

| 06.2014 | 1.0.6                | Different names of signals are fixed: SYNC_IN, SYNC_OUT is changed to START_IN, START_OUT, accordingly.                                                                                                                                                                  |

| 05.2015 | 1.0.7                | Added item 3.3.5, item . 5.5.1                                                                                                                                                                                                                                           |

| 03.2016 | 1.0.8                | Added Chapter 7                                                                                                                                                                                                                                                          |

| 02.2017 | 1.0.9                | Paragraph added 3.3.4.1                                                                                                                                                                                                                                                  |

| 07.2017 | 1.0.10               | A warning is added to item. 3.3.5.2                                                                                                                                                                                                                                      |

| 10.2017 | 1.1.0                | Added industrial design versions.The characteristics according to the resultsof preparation of the family of <i>L-CARD voltage measuring</i> converters for certification as Means of Measurement are broughtinto correspondence.Added to item 3.3.8.Paragraph added 4.5 |

Revision history of this document

When reading this document electronically, to facilitate navigation, use the electronic tree of the table of contents (for example, Acrobat Reader), as well as hyperlinks within the document.

# Contents

| CHAPTER 1. GENERAL DESCRIPTION                                                                                                       | 7  |

|--------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>1.1. Order information</b>                                                                                                        |    |

| 1.2. Consumer properties of L-502 in comparison with L-780(M), L-783(M), L-79                                                        |    |

| <b>1.3.</b> Appearance and main structural elements                                                                                  | 11 |

| 1.4. Documentation structure for L-502                                                                                               | 13 |

| CHAPTER 2. INSTALLATION AND CONFIGURATION.                                                                                           | 14 |

| 2.1. Configuration L-502.                                                                                                            | 14 |

| 2.1.1. Backup boot configuration                                                                                                     |    |

| 2.1.2. The configuration of the outputs DAC1 and DAC2                                                                                |    |

| 2.1.3. Configuring the resolution of the active state of the digital outputs                                                         | 15 |

| 2.2. Installing the L-502 in your computer                                                                                           | 16 |

| 2.3. Function of the status LED on the front panel                                                                                   | 16 |

| 2.4. Serial number. L-502 version number. Module identification in a multi-modul                                                     | e  |

| configuration                                                                                                                        |    |

| 2.5. Software installation                                                                                                           | 18 |

| CHAPTER 3. THE DEVICE AND PRINCIPLE OF OPERATION L-502                                                                               | 19 |

| 3.1. Conventions                                                                                                                     | 19 |

| 3.1.1. Convention on numbering                                                                                                       |    |

| 3.1.2. The assumption on the concept of "frequency"                                                                                  |    |

| 3.1.3. The agreement on the terms "card", "board" and "module"                                                                       | 19 |

| 3.2. Introduction (L-502 concept)                                                                                                    | 19 |

| 3.3. Operation principle                                                                                                             | 22 |

| 3.3.1. Reference frequency                                                                                                           |    |

| 3.3.2. ADC channel                                                                                                                   |    |

| 3.3.3. Digital input channel                                                                                                         |    |

| 3.3.4. Digital output and DAC channels                                                                                               |    |

| 3.3.5. General principle for synchronization in L-502                                                                                |    |

| 3.3.6. Setting the ratio between the time of setting the signal and the resolution for each                                          |    |

| channel of the ADC is a unique possibility of the L-502!                                                                             |    |

| <ul><li>3.3.7. Relative switching delays in ADC channels.</li><li>3.3.8. Relative delays of the ADC, DAC and I/O channels.</li></ul> |    |

| 5.5.6. Relative delays of the ADC, DAC and 1/O channels                                                                              | 29 |

4

| <b>3.4.</b> Operation principle and function circuit                               |           |

|------------------------------------------------------------------------------------|-----------|

| CHAPTER 4. CONNECTION OF SIGNALS.                                                  | 33        |

| 4.1. GND, DGND, AGND circuits                                                      |           |

| 4.2. L-502 connectors description.                                                 |           |

| 4.2.1. L-502 external signal connector.                                            |           |

| 4.2.2. Connecting the cable shield                                                 |           |

| 4.2.3. Internal signal L-502 connector.                                            |           |

| 4.2.4. Internal connector of intermodule synchronization.                          |           |

| 4.2.5. JTAG connector.                                                             |           |

| 4.3. The maximum allowable conditions at the inputs and outputs of signal line     | s 42      |

| 4.4. ADC input operation voltage range                                             |           |

| 4.5. Necessary conditions for correct connection and correct settings of the input | ut of the |

| ADC L-502.                                                                         |           |

| 4.5.1. The physical causes of possible problems                                    |           |

| 4.5.2. Conditions for correct connection and settings L-502                        |           |

| 4.6. Calculation of the total load power of L-502 output circuits                  |           |

| CHAPTER 5. SPECIFICATIONS                                                          | 49        |

| 5.1. ADC                                                                           |           |

| 5.1.1. Limits of the permissible relative basic error of measuring the AC voltage  |           |

| 5.1.2. ADC own input noise.                                                        | 51        |

| 5.1.3. ADC inter-channel passing                                                   | 51        |

| 5.2. DAC                                                                           | 52        |

| 5.2.1. AC voltage playback error                                                   |           |

| 5.3. Digital inputs                                                                | 53        |

| 5.4. Digital outputs                                                               | 54        |

| 5.5. Synchronization in L-502                                                      |           |

| 5.5.1. Synchronization characteristics                                             |           |

| 5.5.2. Intermodule synchronization interface                                       | 55        |

| 5.6. Characteristics of standard interfaces                                        |           |

| 5.7. Power supply system and galvanic isolation.                                   |           |

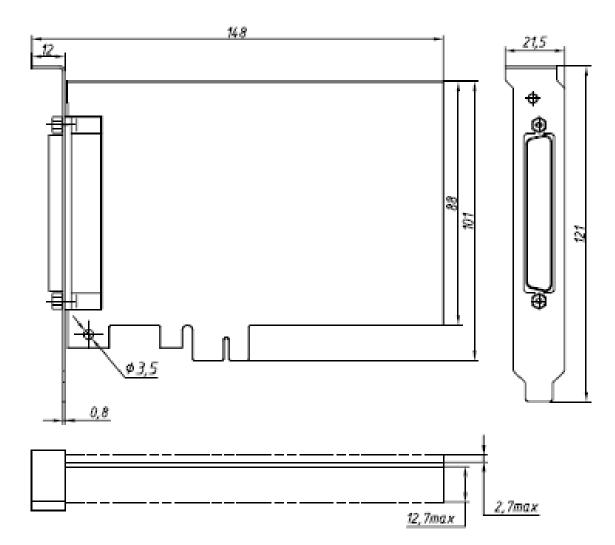

| 5.8. Construction specification                                                    | 58        |

| 5.9. Environmental conditions                                                      |           |

| 5.9.1. Normal conditions                                                           |           |

| 5.9.2. Operating conditions                                                        | 58        |

| CHAPTER 6. CONNEXION SAMPLES                                                       | 59        |

| <b>6.1.</b> A | DC entry point connection                                                              | 59  |

|---------------|----------------------------------------------------------------------------------------|-----|

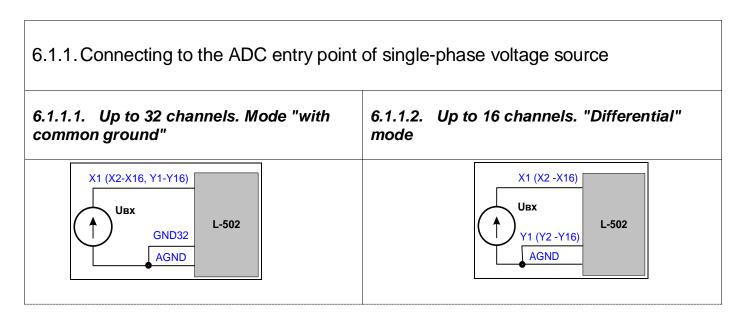

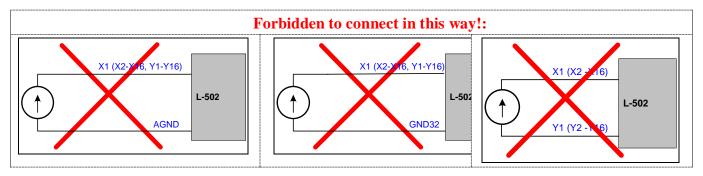

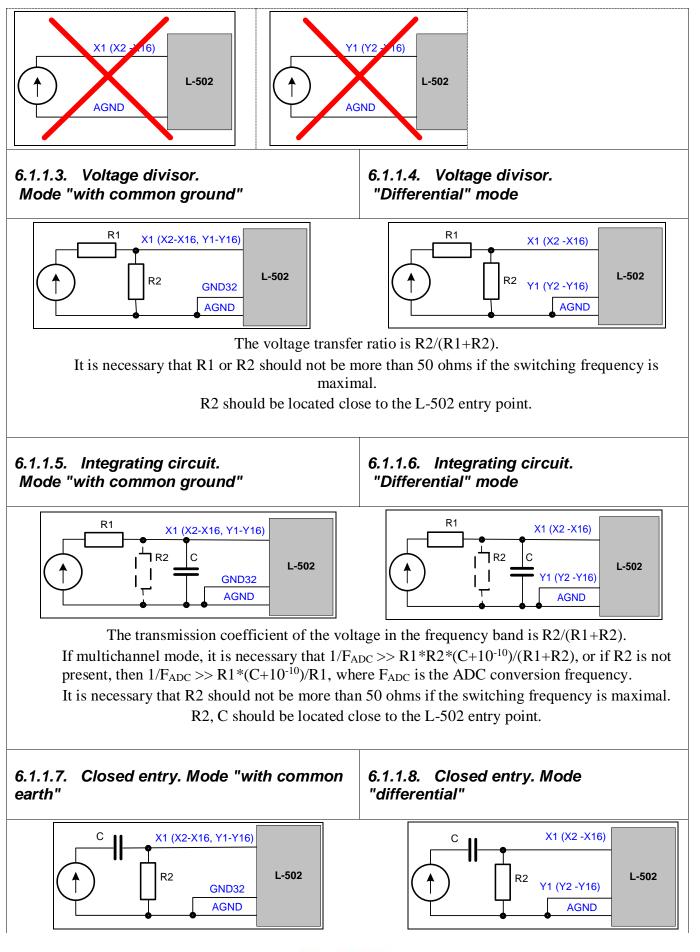

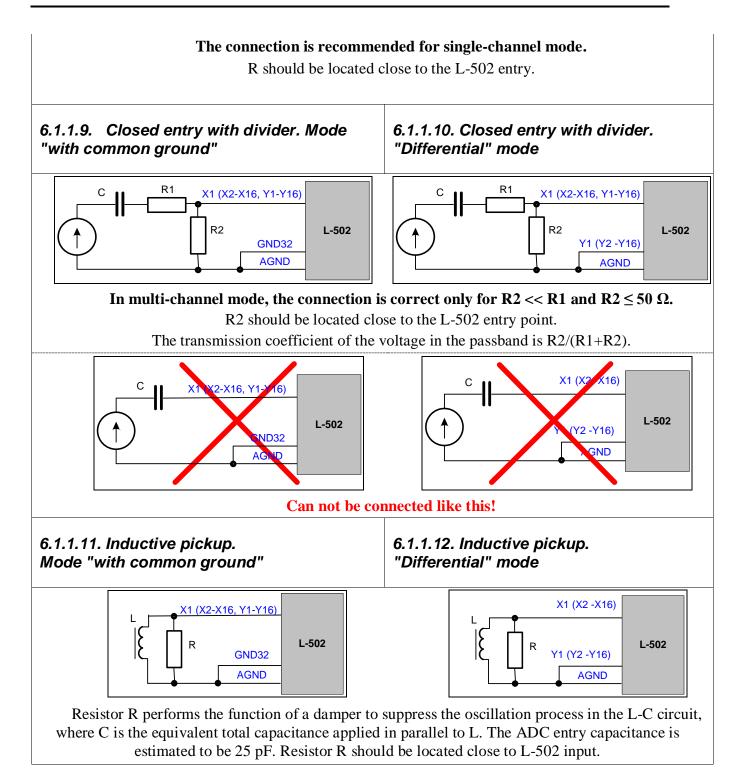

| 6.1.1.        | Connecting to the ADC entry point of single-phase voltage source                       | 59  |

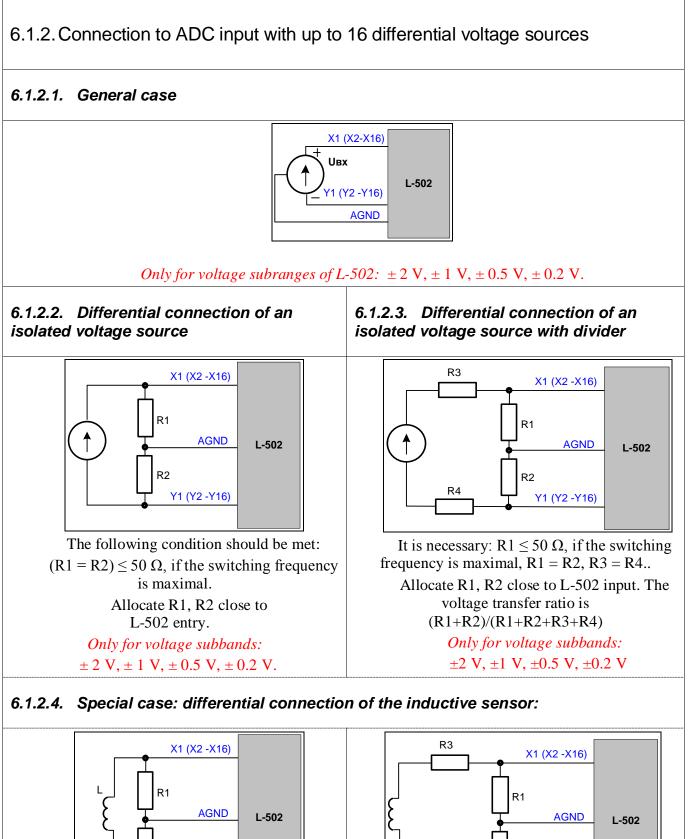

| 6.1.2.        | Connection to ADC input with up to 16 differential voltage sources                     | 62  |

| 6.1.3.        | Connection to the ADC input for the case where the common wire of the signal           |     |

| sources has a | offset potential Ucm of max. ± 1 V relative to the AGND circuit                        | 53  |

| 6.1.4.        | Measurement of the voltage drop on the circuit section in the differential mode (up to | 0   |

| 16- channels  |                                                                                        |     |

|               | Differential connection of the transformer (throttle) winding with midpoint and offse  |     |

|               | h respect to AGND                                                                      | 54  |

|               | Example of mixed connection of voltage sources "with common ground" and                |     |

| differential. | 64                                                                                     |     |

|               | Connecting a power supply to the ADC input                                             |     |

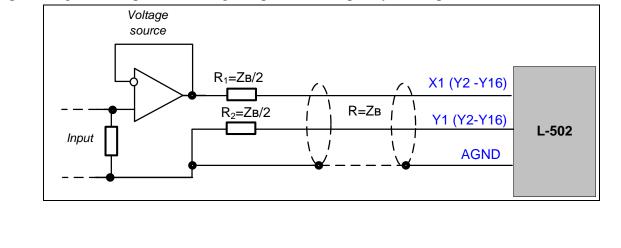

|               | Consistent connection of remote current sources or voltage through a long line with    |     |

|               | nce of Zw with load on the side of the receiver                                        |     |

|               | Differential connection of an isolated current source or voltage                       | 56  |

|               | The coordinated connection of a remote voltage source through a pair of long line      |     |

| with a wave   | resistance Zw with matching on the signal source side                                  | 57  |

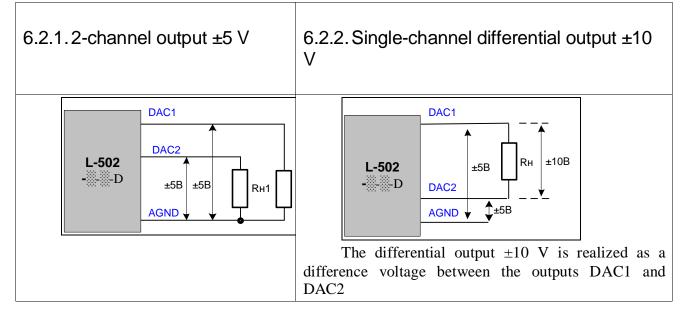

| 6.2. (        | Connecting the DAC outputs                                                             | 68  |

|               | 2-channel output ±5 V                                                                  |     |

|               | Single-channel differential output ±10 V                                               |     |

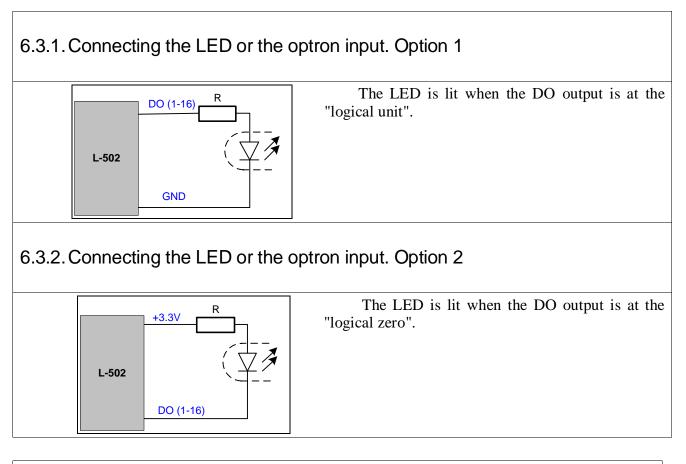

| 6.3. (        | Connecting the digital inputs and outputs                                              | 69  |

| 6.3.1.        | Connecting the LED or the optron input. Option 1                                       |     |

| 6.3.2.        | Connecting the LED or the optron input. Option 2                                       |     |

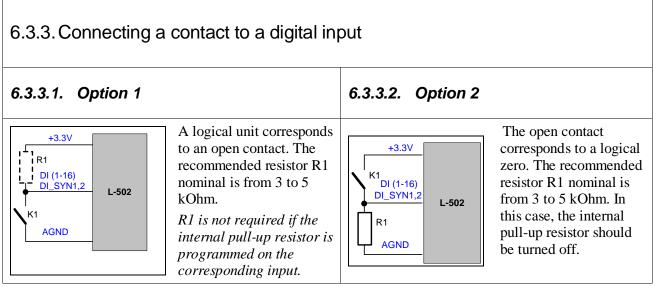

| 6.3.3.        | Connecting a contact to a digital input                                                | 59  |

| BIBLI         | OGRAPHY                                                                                | 72  |

| LIST          | OF TABLES                                                                              | 72  |

| LIST          | OF FIGURES                                                                             | 72  |

| CONT          | ENTS                                                                                   | . 4 |

## Chapter 1. General description.

L-Card data acquisition system L-502 based on the PCI Express interface of modern computer motherboards. L-502 – this system of the proprietary development of the "L-Card" LLC, it is made on the basis of high-tech production of the company, it provides its own technical support and maintenance.

#### The most important characteristics of L-502:

- ADC: 16 bits, conversion frequency up to 2 MHz, with switching to 16 differential channels or 32 channels with common ground. Subranges: ±10 V", "±5 V", "±2 V", "±1 V", ±0.5 V, ±0.2 V.

- DAC (optional): 16 bits, 2 channels, output ± 5 V, asynchronous or synchronous mode with a conversion frequency of up to 1 MHz for each channel.

- Digital input: up to 18 digital inputs of general purpose, asynchronous or synchronous data collection mode with a frequency of up to 2 million words per second.

- Digital output: up to 16 digital outputs of general purpose, with separate control of the output resolution of the high and low byte, asynchronous or synchronous data output mode with a frequency of up to 1 million words per second.

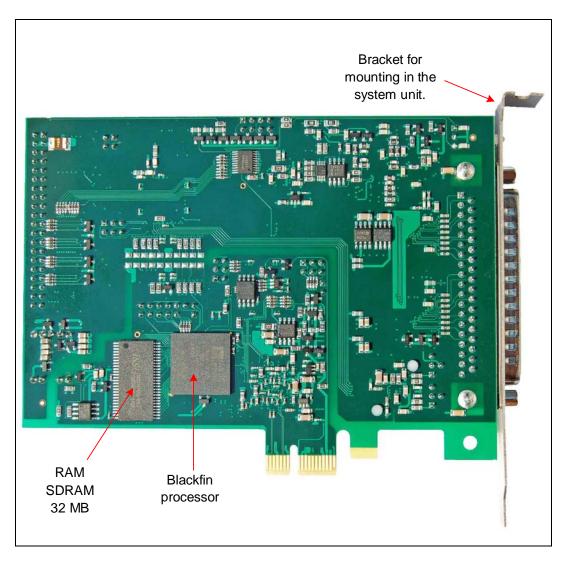

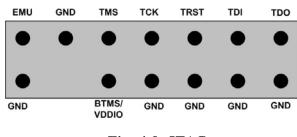

- Processor Blackfin 530 MHz, 32 MB RAM, JTAG input (optional) allows you to use the ready "advanced" signal processing and control functions inside the **L-502** or independently engage in low-level programming of these functions.

- Galvanic isolation (optional) provides isolation of digital and analog signal inputs/ outputs to all circuits of the computer.

The above "optional" is reflected in the L-502 module designation system on fig. 1-1.

The system can consist of one or more modules (boards) **L-502**, synchronized from each other, from an internal or external synchronization source.

Fig. 1-1. Symbol system for L-502 module

## 1.1. Order information

Available modifications for L-502 for the order:

L-502-P-G-D-I

L-502-P-G, L-502-P-G-D

L-502-X-G, L-502-X-G-D

L-502-X-X. L-502-X-X-D

When choosing the modification of the L-502 module for the order, it should be noted that when you contact the L-Card sales department, the previously purchased version of the L-502 module can be modified only in the direction of installing the DAC. In other words, only the following modifications of the L-502 modules are technically recognized:

$L-502-P-G \rightarrow L-502-P-G-D$

$L-502-X-G \rightarrow L-502-X-G-D$

$L-502-X-X \rightarrow L-502-X-X-D$

This work on the installation of a DAC can be carried out exclusively in the L-Card, while the original warranty period of 1.5 years for the product L-502 is retained.

1.1.1. Order kit

- 1. Module L-502 (in accordance with the ordered modification)

- 2. Cable part of DB-37F connector;

- 3. Cover for DP-37 connector

- 4. Jumper for configuration of outputs (3 pieces are pre-installed on the board + 2 pieces in the kit).

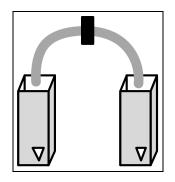

- 5. The synchronization cable *is supplied separately*. The cable is used to connect two L-502 modules. In the general case, for the connection of N pcs. of L-502 modules on one motherboard, you will need (N-1) pcs. of synchronization cables.

# 1.2. Consumer properties of L-502 in comparison with L-780(M), L-783(M), L-791

The new family of **L-502** in its overall technical characteristics is the development of the line **L-780** (**M**), **L-783** (**M**), **L-791** at a higher technological level. There is considerable compatibility of **L-502** in the type and purpose of the contacts of signal connectors, but, unfortunately, there is no software compatibility with them. The **L-502** module is more versatile in its capabilities as it practically covers the range of tasks that was solved earlier within the framework of the 700th family, in addition, it offers fundamentally new opportunities. A comparison of the technical characteristics of the **L-502** module with its predecessors of the 700th family is shown in table 1-1. The following conventions are adopted in the table, which are consistent with the versions of modifications L-502 in accordance with fig. 1-1:

- [P] only for L-502-P- (with processor)

- [P] only for L-502-X- (without processor)

- [G] only for L-502- -G- (with galvanic isolation)

| Characteristics                                                  | L-502                                           | <u>L-780(M)</u>           | <u>L-783(M)</u>                        | <u>L-791</u>                                                                      |

|------------------------------------------------------------------|-------------------------------------------------|---------------------------|----------------------------------------|-----------------------------------------------------------------------------------|

| Bit depth:                                                       |                                                 |                           |                                        |                                                                                   |

| - ADC                                                            | 16 <sup>1</sup>                                 | 14                        | 12                                     | 14                                                                                |

| - DAC                                                            | 16 [D]                                          | 12                        | 12                                     | 12                                                                                |

| - Dig. input                                                     | 18                                              | 16                        | 16                                     | 16                                                                                |

| - Dig. output                                                    | 16                                              | 16                        | 16                                     | 16                                                                                |

| Max. speed of o/i, in synchronous mode, n. count./s <sup>2</sup> |                                                 |                           |                                        |                                                                                   |

| - ADC                                                            | 2000                                            | 400                       | 3000                                   | 400                                                                               |

| - DAC (for each channel)                                         | 1000 [D]                                        | 100                       | 100                                    | 100                                                                               |

| - Digital input                                                  | 2000                                            | No sync                   | chronous mode                          | 400                                                                               |

| - Digital output                                                 | 1000                                            |                           | No synchronous r                       | node                                                                              |

| ADC channels                                                     | 160                                             | lifferential/ 32 wit      | h common ground                        |                                                                                   |

| ADC subranges, V                                                 | $\pm 10, \pm 5, \pm 2, \pm 1, \pm 0,5, \pm 0,2$ | ±5, ±1,25,<br>±0,3, ±0,08 | $\pm 5, \pm 2, 5, \pm 1, 25, \pm 0, 6$ | $\pm 10, \pm 5, \pm 2,5, \\ \pm 1,25, \pm 0,6, \\ \pm 0,3, \pm 0,15, \\ \pm 0,07$ |

| ADC common-mode signal range, V                                  | ±1                                              | ±5                        | ±5                                     | ±10                                                                               |

| DAC range, V                                                     | ±5                                              | ±5                        | ±5                                     | ±5                                                                                |

| (output current, mA)                                             | (10) [D]                                        | (1)                       | (1)                                    | (1)                                                                               |

| The word width of the module data, bit                           | 32                                              | 16                        | 16                                     | 32                                                                                |

| Multiple-frequency capability of data collection                 | Yes [P]                                         | No                        | No                                     | Yes                                                                               |

| Index <sup>3</sup> data format                                   | Yes                                             | No                        | No                                     | No                                                                                |

| Internal data calibration                                        | Yes [P].<br>Only for ADC [₽]                    | Only for ADC              | Only for ADC                           | No                                                                                |

| Ability to set ADC channel resolution/ timing                    | Yes                                             | No                        | No                                     | No                                                                                |

| Processor (core clock)                                           | ADSP-BF523                                      | ADS                       | P-2185(M)                              | No                                                                                |

|                                                                  | (530 MHz) [P]                                   | 29,5 MHz                  | 40 MHz                                 |                                                                                   |

| Processor's external RAM                                         | 32 MB [P]                                       | No                        | No                                     | No                                                                                |

#### Table 1-1. Comparison with L-502 c L-780(M), L-783(M) and L-791

<sup>&</sup>lt;sup>1</sup> From the L-502, ADC data, expanded to 24 bits as a result of arithmetic processing, is transferred to the computer.

<sup>&</sup>lt;sup>2</sup> A reference is the full word of the data of the ADC, DAC or input/ output with the bit width adopted in this product.

<sup>&</sup>lt;sup>3</sup> When the data word format contains information about the channel number

| Characteristics                                                                           | L-502                     | <u>L-780(M)</u>           | <u>L-783(M)</u>           | <u>L-791</u>             |

|-------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| The amount of user area of Flash-memory                                                   | 1 MB                      | 32 bytes                  | 32 bytes                  | 64 Kbyte                 |

| JTAG port to adjust the<br>embedded software                                              | Yes<br>[P]                | No                        | No                        | No                       |

| The possibility of custom low-<br>level programming                                       | Yes                       | Yes                       | Yes                       | No                       |

| Independent software access to<br>the memory of the signal<br>processor                   | Yes<br>[P]                | Yes                       | Yes                       | No                       |

| DMA in PCI BUS MASTER<br>mode                                                             | Yes                       | No                        | No                        | Yes                      |

| Interface                                                                                 | PCIe x1                   | I                         | PCI 32 bit, slot 5V       |                          |

| Synchronization:                                                                          |                           |                           |                           |                          |

| - External data collection start                                                          | Yes                       | Yes                       | Yes                       | Yes                      |

| - External frequency of ADC                                                               | Yes                       | No                        | No                        | No                       |

| conversion                                                                                | Yes                       | No                        | No                        | No                       |

| <ul><li>From the next module</li><li>Analogous</li></ul>                                  | Yes                       | Yes                       | Yes                       | No                       |

| The technology of the basic interface element                                             | FPGA<br>Altera Cyclone IV | PLX Tech.<br>PLX9050/9030 | PLX Tech.<br>PLX9050/9030 | FPGA<br>Altera<br>Acex1K |

| Indication on the panel                                                                   | Yes                       | No                        | No                        | No                       |

| The possibility of remote firmware update FPGA                                            | Yes                       | No                        | No                        | Yes                      |

| Program activation of pull-up resistors of digital inputs                                 | Yes                       | No                        | No                        | No                       |

| Independent resolution of the active state of the digital output of the low and high byte | Yes                       | No                        | No                        | No                       |

Full list of L-502 characteristics – Chapter 5 on page 49.

Already today, the architecture of the L-502 is not limited to just this one project by L-Card LLC. The new <u>E-502</u> with USB and Internet interfaces has a continuity of architecture with <u>L-502</u>: Only the interface with the PC with the same functionality as the L-502 was subjected to processing, except for small functional differences. The E-502 and L-502 software also has continuity (common library functions of the upper software level of the PC, identical to

the software at the Blackfin level).

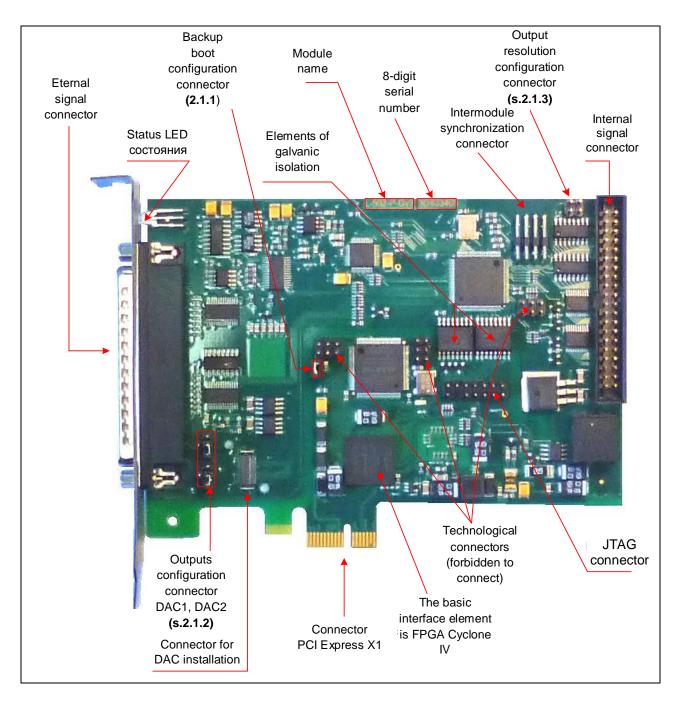

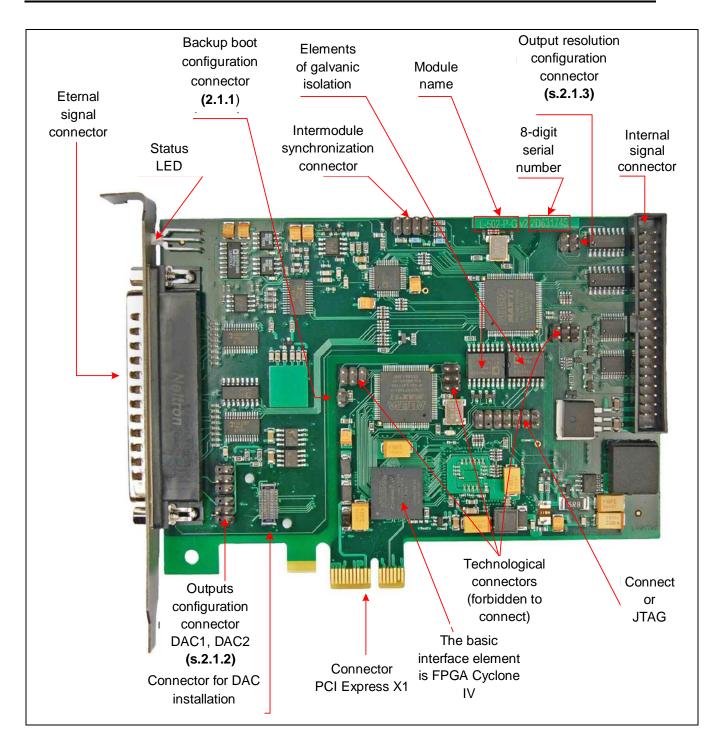

## 1.3. Appearance and main structural elements

Depending on the version of the module (item 2.4, p.17), there are differences in the location of the inter-module sync connector and the output enable connector. Unlike the previous versions, in version 3, an angular synchronization connector is used, which allows connecting the synchronization cable when the L-502 module is already inserted and fixed in the system unit along with the installed adjacent PCI-Express modules.

Fig.1-2. L-502 version 3 (face layout)

Fig. 1-3. L-502 version 1 or 2 (face layout)

Fig.1-4. L-502 (back layout)

## 1.4. Documentation structure for L-502

A complete guide to the L-502 is divided into four separate books:

- L-502. User Manual

- L-502. Programmer Manual

- L-502. Connexion samples

- L-502. Low-level description

# Chapter 2. Installation and configuration.

## 2.1. Configuration L-502.

Here, the hardware settings of the L-502 are considered, which must be done before the L-502 module is installed in the computer. These settings are made by jumper, which you need to put (or not) on the corresponding pair of contacts, indicated below in the tables with conditional numbers.

#### 2.1.1. Backup boot configuration

|   | Jumper for<br>1-2 | FPGA is loaded with the main firmware from the Flash-memory.<br>This loading mode is considered the main mode, and the L-502 always comes with a jumper set to contacts 1-2.                                                                                                                                       |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | No jumper         | FPGA is loaded with a backup copy of the firmware from Flash-memory.<br>This loading mode is considered auxiliary and the user can apply it if, for some reason, the main flash memory firmware has been corrupted and, as a result, the L-502 device has ceased to be detected by the operating system. See Note. |

**Note**: Putting or removing the backup jumper should be done with the computer system's completely de-energized computer (the usual shutdown of the computer - the software or the button at the front of the system unit - is not enough, since the system unit has the "standby" power)

|       | No jumper on 3,4,5,6  | The contact "DAC1" is not<br>connected to the external signal<br>connector, see item 4.2.1, p. 33 |

|-------|-----------------------|---------------------------------------------------------------------------------------------------|

|       | Jumper on 3-4         | The contact "DAC1" on the<br>connector is connected to the<br>DAC - channel 1                     |

| 5 3 3 | Jumper on 3-5         | The contact "DAC1" on the connector is connected to +15V                                          |

|       | Jumper on 3-6         | The contact "DAC1" on the connector is connected to AGND                                          |

|       | No jumper on 7,8,9,10 | The contact "DAC2" is not connected on the connector                                              |

|       | Jumper on 7-8         | The contact "DAC2" on the connector is connected to the DAC - channel 2                           |

|       | Jumper on 7-9         | The contact "DAC2" on the connector is connected to -15V.                                         |

|       | Jumper on 7-10        | The contact "DAC2" on the connector is connected to the DGND <i>digital ground</i> circuit.       |

## 2.1.2. The configuration of the outputs DAC1 and DAC2

## 2.1.3. Configuring the resolution of the active state of the digital outputs

| For version 1 or 2 : | Jumper on 11-12       | Forced output enable of the low-<br>order byte, see 4.2.3, p.36.               |

|----------------------|-----------------------|--------------------------------------------------------------------------------|

| 11 12 12 14          | No jumper on<br>11-12 | The resolution of the low byte output depends on the program setting.          |

|                      | Jumper on 13-14       | Forced output enable of high byte.                                             |

| For version 3:       | No jumper on<br>13-14 | The output enable of the high<br>byte depends on the program<br>configuration. |

|                      |                       |                                                                                |

| 11 12<br>13 14<br>100000000000000000000000000000000000 |  |  |

|--------------------------------------------------------|--|--|

|--------------------------------------------------------|--|--|

## 2.2. Installing the L-502 in your computer

The L-502 module can be installed in any PCI Express card slot of any size (x1, x2, x4, x8, x12, x16 and x32) from 1.0 to 3.0.

Before installing the L-502 in the computer, set the configuration jumper to the desired position, i. 2.1.

To install, and also to remove L-502 is allowed only when the computer's system unit is deenergized. "Hot connection" is not supported!

It is recommended to install L-502 in the system block with good air circulation in the interior.

It is recommended to avoid electrostatic discharges during the installation of L-502 in the computer. When handling the L-502, keep the module behind the metal panel.

It is not recommended to install the L-502 in an adjacent slot next to the heating radiator of an adjacent module, for example, in the vicinity of a powerful graphics card.

The two 6-threaded screws on the L-502 bracket must be tightened securely, make sure of this before installing the L-502.

The design of the L-502 is in strict accordance with the requirements of the PCI Express specification. But in the real case, it is also important: the quality of the computer chassis, the errors in installing the motherboard in the computer, the design features of the particular motherboard, the design features of the card in the adjacent slot. Due to a combination of these factors when installing L-502, you may encounter contacting the radiators of the motherboard (and other structural elements) with the internal electrically conductive elements L-502. It should be specially noted:

Do not touch the L-502 conductive elements with any other electrically conductive elements of the motherboard or adjacent PCI/ PCI-E cards.

It is not allowed to operate the L-502 with an unsupported bracket. The standard mounting screws for the card brackets (or plugs) are usually included in the computer case kit.

## 2.3. Function of the status LED on the front panel.

In the usual case, the LED on the front panel indicates the following statuses of the module:

| LED status | Description                                          |

|------------|------------------------------------------------------|

| Red light  | L-502 is on and in the synchronous I/O standby mode. |

| Green light | L-502 is in the synchronous I/O mode. |

|-------------|---------------------------------------|

| No lights   | Power is off.                         |

If more than one L-502 module is used in the computer's system unit, the task is to identify the module with which the program is currently running. To solve this problem, the software function of controlling the red glow of the LED is provided. Naturally, the same problem can be solved by software reading the serial number of the module, however, a comparison with the number punched on the board will require the opening of the system unit, which is inconvenient for operation.

# 2.4. Serial number. L-502 version number. Module identification in a multi-module configuration

The unique eight-digit product serial number item 1.3, page 11 serves to identify the module instance throughout the life cycle. The L-502 serial number is program-accessible.

The first digit of the serial number corresponds to the version number of the product L-502. The product version is changed to improve the design and technological characteristics during the production "life cycle" of the product. All versions of L-502 are programmed and functionally identical.

The task of module identification in a multi-module configuration arises because PCI Express (as well as PCI) -interface historically has never had a software binding to the physical position of the module in the slot line, and this binding occurs in operating systems when the system is initialized. If the composition of the equipment has not changed (and all the equipment remains operative), then there is a hope that the assignment of resources in the system during the initialization should occur from one computer to another. But in order to reliably compare a particular instance of the module and its assigned address *in a multi-module user program, it is necessary to bind to the serial number of the L-502 module*.

## 2.5. Software installation

To install the necessary drivers and libraries for Windows OS, you must download and run the installer "L-Card L502 / E502 SDK" <u>http://www.lcard.ru/download/lpcie\_setup.exe</u>.

For information on installing the driver and libraries under Linux OS, see <u>the</u> <u>Programmer Guide</u>, <u>http://www.lcard.ru/download/x502api\_en.pdf</u>.

# Chapter 3. The device and principle of operation L-502.

## 3.1. Conventions

#### 3.1.1. Convention on numbering

In all products of the L-Card, the numbering of all physical objects (for example, channel numbers) in the description of the principle of action and design is always made from one!

This agreement is completely unrelated to the encoding method in programming, where the numbers of these physical objects can be encoded from scratch or otherwise, in the context of the corresponding library function or programming language.

#### 3.1.2. The assumption on the concept of "frequency"

In the documentation for L-502, the frequency of discrete signals (for examples, synchronization signals) is expressed in Hertz, rather than in periods per second, as is customary in the classical sense of frequency for a non-sinusoidal process.

#### 3.1.3. The agreement on the terms "card", "board" and "module"

Literary PCI or PCI-E is translated as a card (in this case, even a L-card <sup>(i)</sup>). But many call it a board. Following the terms, in this manual we will adhere to the more strict name of this constructive unit, adopted in the ESKD - module. In particular, we will start from this point by using the term "multimodule synchronization".

### 3.2. Introduction (L-502 concept)

For the users who have already used L-780(M), L-783(M), L-761, L-791, the new device L-502 looks more like the development of this product line (L-7xx) at the new technical level. On the other hand, it can not be asserted that L-502 is an analog of one of these products or that L-502 is the mechanical sum of all the best characteristics of these products. Most likely, the L-502 project is the result of an analysis of the user needs in the market segment of the above products and the result of an engineering compromise at a modern technical level, where the most popular characteristics in this product line were first taken into account for most applications in order to obtain the best price-quality ratio.

L-502 has 6 modifications (fig. 1-1, item 1.1) which are based on the same multilayer printed board. Modification is achieved by different variants of the factory assembly. If you previously purchased an L-502 without a DAC, then the L-Card accepts orders for the installation of a DAC. The remaining options for subsequent changes of the L-502 modifications are not considered technically feasible.

The presence of the ADSP-BF523 signal processor with RAM (modification L-502-P-)) is considered justified for those users who want to get a maximum of on-board signal processing capabilities on-board, as well as advanced users to have their own low-level processor programming, possibly using a JTAG emulator.

The presence of galvanic isolation (modification L-502--G--G) is considered necessary if the sources of L-502 input signals and the load circuit of the output signals are not isolated from the ground and, at the same time, directly (electrically short) are not connected to the case of the system unit. The galvanic isolation in L-502 provides isolation of all circuits on the contacts of the internal and external signal connectors and the inter-module synchronization connector (fig. 1-3) relative to all circuits of the computer. The signal chains are not isolated between each other.

The presence of a 2-channel DAC (modification L-502---D) is necessary if in your task it is necessary to reproduce the output analog voltage levels or temporary voltage functions.

ADC 16 bits with a conversion frequency of up to 2 MHz with 16/32-channel circuit switching (up to 16 differential channels, up to 32 with a common ground) with voltage subbands  $\pm$  10 V,  $\pm$  5 V,  $\pm$  2 V,  $\pm$  1 V,  $\pm$  0.5 V,  $\pm$  0.2 V has an analogue path improved with regard to L-7xx for the following parameters:

- The resolution of the ADC is increased and the signal-to-noise ratio is improved due to the increase in the ADC bit depth, the quality of the analog path, and also at low data acquisition frequencies due to the built-in hardware averaging of the sample data within the same channel scan cycle.

- The interchannel passage for the same test conditions is reduced together with L-7xx: the same impedances of signal sources and channel switching frequency. In particular, the advantage of L-502 on lower sub-ranges of voltages of  $\pm$  0.5 V,  $\pm$  0.2 V is gigantic with regard to L-7xx for the same application conditions.

- The range is ± 10 V compared to ± 5 V in L-783 (M).

Along with the obvious progress in the characteristics of the ADC in L-502, there are trade-offs in the following characteristics with regard to L-7xx:

- Maximum ADC conversion frequency is limited by 2 MHz (in L-783(M) 3 MHz).

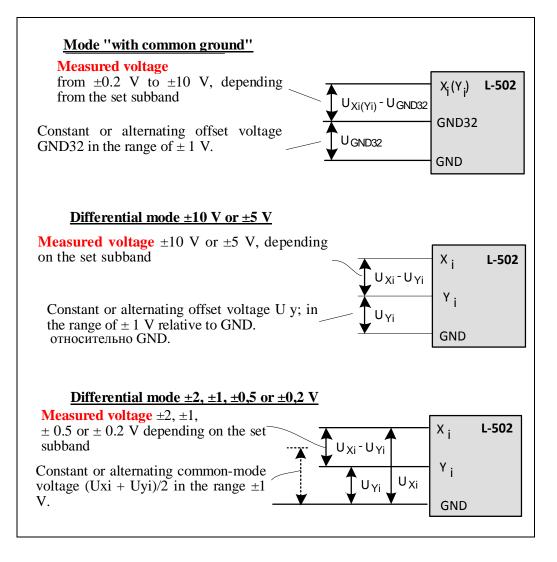

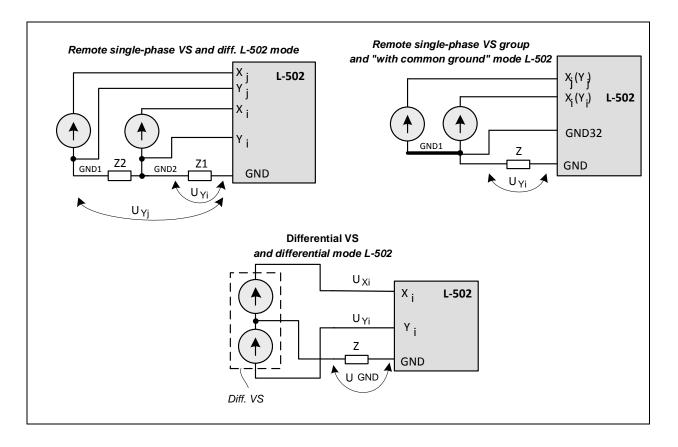

- Limited to  $\pm 1$  V operating range of the input signal at the inputs Y and GND32 (for details, see 4.4).

Instrumental DAC 16 bits 2 channels  $\pm$  5 V compared to DAC 12 bits in L-7xx has a much better resolution, a larger working output current, normalized high-speed transients associated with the transition from one sample to another, which allows using this DAC in applications, the quality of the functional generator required from the DAC<sup>4</sup>. Synchronous (streaming) up to 1 MHz per channel or asynchronous mode on the selected DAC channel is possible, including mixed synchronous-asynchronous mode on different channels.

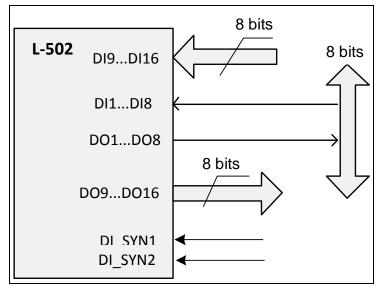

Digital input, up to 18 lines, synchronous mode up to 2 MHz or asynchronous. In synchronous mode, the stream from digital lines is synchronous with the ADC stream, but separate and independent of the settings of the ADC data collection frame (the frequency of data collection by digital lines is set separately and does not depend on the ADC frame settings). Programmable pull-up resistors to a high logic level on digital inputs.

Digital input, 16 lines. Synchronous as synchronous output up to 1 MHz, and asynchronous is possible. With synchronous output, the frequency is matched to the frequency of the DAC output. The output enable allocated for the low and high byte increases the flexibility of using digital lines,

<sup>&</sup>lt;sup>4</sup> Strictly speaking, for qualitative sound applications to the DAC, even more stringent requirements are imposed in comparison with the requirements for the function generators.

for example, configuration is possible: 8-bit 2-way data bus + up to 10 data bits per input + up to 8 data bits per output. This allows the implementation of bus diagrams controlling complex digital devices (item 4.2.3.1, p. 38).

Note the limitations of the asynchronous output for external synchronization (n.3.3.4.1).

The ADC, DAC, digital input and output streams are synchronized with respect to the same  $f_{ref}$  reference frequency, which can be assigned programmatically: 1.5 MHz or 2 MHz.

Hardware-based in L-502, the physical conversion frequency of the ADC and synchronous digital input is always equal to  $\mathbf{f}_{ref}$ , and the physical refresh rate of each DAC channel and digital output is  $\mathbf{f}_{ref}/2$ . Getting all the fractional frequences of the data input  $\mathbf{f}_{ref}/n$  and  $\mathbf{f}_{ref}/2m$  output fractional frequencies (where m and n are natural numbers) occurs at the hardware processing level in the FPGA and/or in the Blackfin processor.

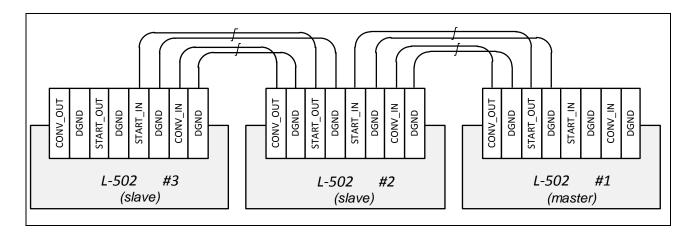

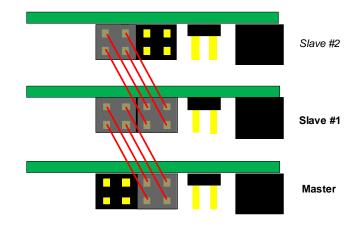

L-502 has a mechanism of inter-module (n.3.1.3) synchronization to form a single synchronous input-output system. Physically, the maximum possible number of L-502 synchronized modules is equal to the number of consecutive free PCI-e slots (of any size) in which L-502 modules are to be installed and the adjacent modules are connected by synchronization cables (the cables are not included in the main kit, they are bought separately). Programmatically, the first L-502 module in the generated synchronization chain is assigned to the master, the others to the slaves. Intermodular synchronization can be arranged for L-502 modules of any modifications, including between L-502 different modifications. It is important to note that if at least one L-502, used in the multi-module synchronization scheme, does not have a galvanic isolation, then all other L-502s lose their galvanic isolation in this scheme (item 4.2.4.1, p.39).

The L-502 has a 32-bit data word format, in which, besides the actual data for input or output, there is also a physical channel number. This hardware binding of the physical channel number ensures that the channel number is mistaken even if the top-level program for some reason lost an arbitrary amount of data.

The PCI Express interface, compared to the PCI interface, has significant user benefits associated with reliability: low-level network protocol PCI Express has a built-in error control and correction mechanism, invisible at the program level. At the same time, the PCI Express device in the BIOS of the computer is seen as a PCI-device, which basically allows to use the L-502 in all operating systems, starting with DOS!

The BUS MASTER mode used in the L-502 allows you to transfer streaming data to the input and output without the processor on the computer (the data is transferred between the RAM of the computer and L-502 only with the resources of the bridge, the chipset of the computer), while the L-502 module itself is a setup unit (master) of the process of data transfer. This is a cardinal advantage with respect to L-783 (M) in terms of unloading the processor in the computer by streaming data transfer operations. And for a multi-module BUS MASTER system is vital!

For advanced users: HOST DMA access mode to the internal memory of the signal processor ADSP-BF523 allows you to apply an independent access channel to the Blackfin internal memory. This creates a huge convenience - "transparency" with low-level Blackfin programming - to see what happens in Blackfin memory on an independent channel. To some extent, HOST DMA can replace JTAG. By the right convenience of the technology of the independent access channel to the memory of the signal processor was evaluated by users even in products E-440 / E14-440 from L-CARD!

## 3.3. Operation principle

In the section 3.2 the concept of the L-502 project was summarized, where the main principles of the module operation were listed. This section contains further details.

#### 3.3.1. Reference frequency

$f_{ref}$  – a signal reference frequency, from which the conversion processes are synchronized to the ADC, DAC, digital input and digital output. The L-502 uses a common reference frequency that synchronizes the start-up of the ADC, DAC, digital input and digital output to an accuracy of an integer division of this frequency. In L-502, the reference frequency source can be internal (2.0 or 1.5 MHz) or external (with a frequency of not more than 2.0 MHz). In particular, the reference frequency from the adjacent L-502 module can be used to form a synchronous multi-module system.

#### 3.3.2. ADC channel.

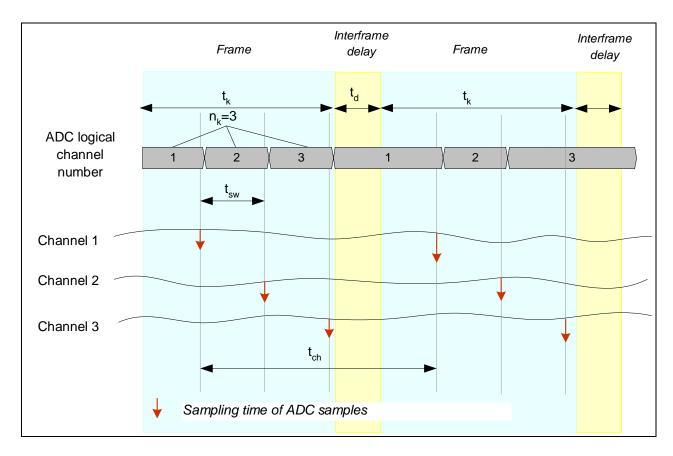

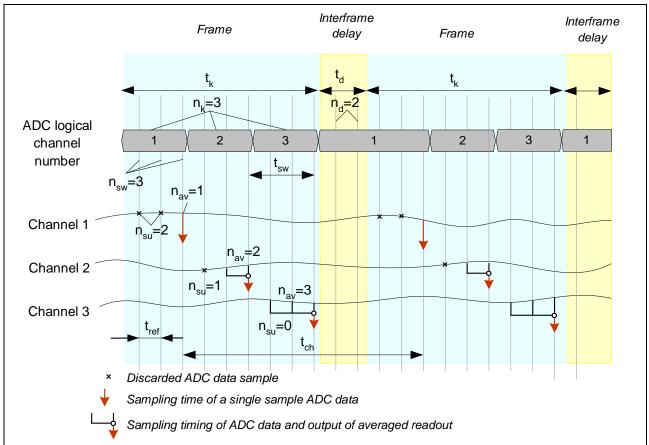

The analog data input channel is a channel with dynamic switching of up to 32 input physical analog channels of the L-502 module to the input of a single internal ADC module. The process of switching channels itself is hardware, according to a pre-configured control table. The input process itself is conditionally divided into periodically alternating frame periods and interframe delay with pre-configured durations of these periods (interframe delay, in particular, can be set to zero). Duration of frame, interframe delay, ADC output sample timing - all these times can be configured, but they are always a multiple of  $t_{ref} = 1/f_{ref}$  - the period of the synchronization reference frequency.

$t_{sw} = n_{sw} / f_{ref}$  – the ADC channel commutation period within the frame, equal to the sampling period of the ADC readouts, where  $n_{sw}$  can be specified by an integer from 1 to 2097152

The preset number of samples in the frame and the size of the control table  $\mathbf{n}_{\kappa}$  can be set from 1 to 256. In each cell of the control table, the physical number of the ADC polling channel is prescribed. Within the frame, the control table will be read completely: from the 1st to the  $\mathbf{n}_{th}$  cell and the read sequence of physical channels will be used in the hardware control mechanism of the channel switch.

The cell number of the control table is called the logical channel number. Accordingly, logical channels can be up to 256, and physical - up to 32. For example, it gives the opportunity to obtain a different frequency of polling different physical channels within the frame.

Frame time:  $\mathbf{t}_{\mathbf{k}} = \mathbf{n}_{\kappa} * \mathbf{t}_{sw} = \mathbf{n}_{\kappa} * \mathbf{n}_{sw} / \mathbf{f}_{ref}$

If necessary, between intermittently following frames, a non-zero interframe delay  $t_d$  with a duration  $n_d$  of synchronization frequency periods can be inserted:

$\mathbf{t}_{d} = \mathbf{n}_{d} * \mathbf{t}_{ref} = \mathbf{n}_{d} / \mathbf{f}_{ref}$ , where  $\mathbf{n}_{d}$  can be set with an integer from 0 to 2097151

The frame period is equal to the sum of the frame length and the interframe delay:

$t_{ch} = t_k + t_d = n_\kappa * \ n_{sw} \ / \ f_{ref} \ + \ n_d / \ f_{ref}$

In other words, the frame period  $t_{ch}$  is equal to the period of data collection from the same logical channel of the control table.

During interframe delay, the sample of control words does not advance, and the analog channel switch is always set in accordance with the first cell of the control table.

Frequency of collection from one logical channel of the control table

$f_{ch} = 1/t_{ch} = f_{ref}/(n_{\kappa}*n_{sw}+n_d),$

where  $\mathbf{f}_{ref}$  can be 2.0 or 1.5 MHz for an internal synchronization or  $\leq 2.0$  MHz for an external,  $\mathbf{n}_{\kappa} = \{1, 2, ..., 256\}, \mathbf{n}_{sw} = \{1, 2, ..., 2097152\}, \mathbf{n}_{d} = \{0, 1, ..., 2097151\}.$

The above-mentioned frame structure of the ADC data is shown in fig. 3-1. Here, for example, a 3-channel ADC mode operation ( $n_{\kappa} = 3$ ) is taken with a non-zero interframe delay  $t_d$ .

Fig. 3-1. Illustration of the personnel principle for acquiring ADC data

#### 3.3.3. Digital input channel.

Synchronous digital input occurs with a period of  $t_{ref} * n_{din}$ ,

where  $n_{din}$  ={1,2,...,2097152} is a configurable frequency division factor for synchronous digital input

#### 3.3.4. Digital output and DAC channels

Synchronous digital output, as well as updating both channels of the DAC, occurs with a period of  $2* t_{ref}$ . If the data buffer for the output and the DAC is empty, then the last value is held at the outputs.

## 3.3.4.1. Restrictions on the current implementation of asynchronous output during external synchronization.

Asynchronous output to digital lines and to DAC in the operating mode will always work when configured for internal synchronization. But asynchronous output to digital lines and to the DAC will not function in the standby mode for external synchronization of the start of data acquisition or waiting for more than 1  $\mu$ s of the external clock of the ADC conversion.

#### 3.3.5. General principle for synchronization in L-502.

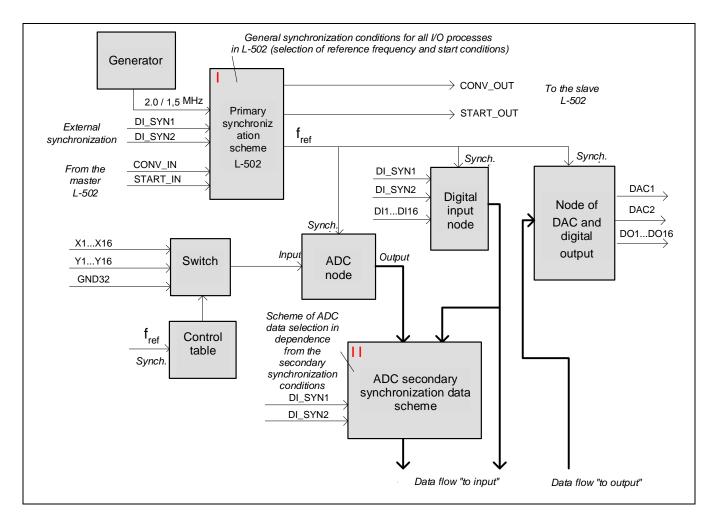

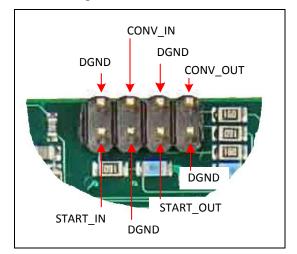

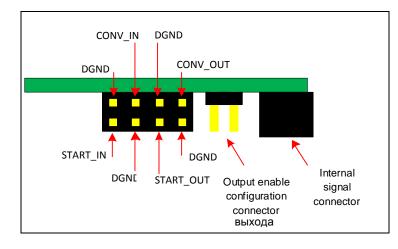

A simplified block diagram is presented on fig. 3-2 to explain the general arrangement of the synchronization system in L-502. L-502 synchronization system consists of two parts: primary and secondary synchronization circuits.

#### 3.3.5.1. Primary synchronization.

The primary synchronization circuit (I) according to the settings selects the corresponding external or internal source of the reference frequency, as well as the external or internal source of the start signal. Using the selected signals, circuit I generates an internal reference signal  $\mathbf{f}_{ref}$  as a sequence of synchronization pulses with a period  $\mathbf{t}_{ref}$ . Moreover, the beginning of this sequence is strictly bound by this scheme to the external or internal *start event*, and all I/O equipment is synchronized (and simultaneously starts) from this sequence: nodes of the ADC (including the logic of the control table), DAC and digital I/O. These nodes contain the corresponding frequency dividers  $\mathbf{f}_{ref}$ .

We list all possible options for user settings related to the *selection of sources of reference frequency signals*:

- The internal generator 2.0/1.5 MHz of this module L-502 (the "default" setting)

- The reference frequency from the DI\_SYN1 input (on the front or on the drop)

- The reference frequency from the DI\_SYN2 input (on the front or on the drop)

- The reference frequency is from the CONV\_IN input from the neighboring L-502, which acts as the master.

We list all possible options for user settings for *selecting sources of the start event of the L-502* I/O system:

- Program start from PC (default setting)

- On the signal from the input DI\_SYN1 (on the front or on the drop)

- On the signal from the input DI\_SYN2 (on the front or on the drop)

- By the signal from the input START\_IN from the neighboring L-502, which acts as the master.

Each L-502 module always translates via its CONV\_OUT and START\_OUT outputs, respectively, its internal reference and start signals for one L-502 slave module, if it is connected to these outputs via a *synchronization cable* and is located in the neighboring PCIe slot of the PC system unit.

The L-502 module can simultaneously be the master for the neighboring L-502 located on one side of this PCI-E slot and slave for the other neighboring L-502 on the opposite side. Thus, synchronization of several L-502, connected by a chain, is supported in an amount limited by the number of PCI-E-s of one PC motherboard.

The primary synchronization circuit provides synchronization of the frequency and phase of the ADC, DAC and cycle cycles of the digital input and output system. It is understood that in a

multi-module synchronization system, the user will be able to intelligently set the control tables of different modules, as well as the division of the reference frequency for the required input-output processes.

•

Note that for the slave L-502 there is a frequency limitation on the input CONV\_IN - no more than 1.5 MHz. Thus, two or more L-502 slave modules can be synchronized only at a reference frequency of 1.5 MHz from the master.

Stopping the primary synchronization scheme is done only programmatically and asynchronously.

Fig. 3-2. L-502 synchronization system structure

#### 3.3.5.2. Secondary synchronization.

•

The functionality of the secondary synchronization is embedded in the project, but is not currently implemented. You can find out about the availability of this functionality in the sales department of L-Card.

The secondary synchronization circuit (II) is the ADC data selection circuit depending on the secondary synchronization conditions, operating exclusively against the background of the previously started clock signal from the output of the primary synchronization circuit (I), i.e. against the background of the started data stream of the ADC.

The following ADC data resolution synchronization modes are supported:

- No synchronization (transparency mode)

- Synchronization from an analog signal in the selected ADC channel

- Digital synchronization with the selected signal from the inputs DI1 ... DI16, or DI\_SYN1, or DI\_SYN2

The following modes of sensitivity to the fluctuations of the synchronization signal are supported:

- Enable of ADC data *on the edge (drop)* of an analog or digital signal

- Enable of ADC data at *a level* "above the threshold" or "below the threshold" (for analog synchronization) or *at the logic level* "1" (for digital synchronization)

The following ADC data inhibit modes are supported:

- Software prohibition (stop) with the possibility of re-authorization (if the previously set enable condition is repeated) without restarting the primary synchronization scheme

- Automatic prohibition (stop) after entering the specified number of frames (from 1 to 2<sup>32</sup>-1 frames) with the possibility of re-authorization (if the previously set resolution condition is repeated) without restarting the primary synchronization scheme

# 3.3.6. Setting the ratio between the time of setting the signal and the resolution for each channel of the ADC is a unique possibility of the L-502!

Above was the principle of the frame-by-line input of ADC data, which was applied in all L-CARD ADCs with the input channel switch, up to synchronization frequency, frame size and interframe delay. But with L-502 this principle is developed for better adaptation to the output physical properties of the signal source. Further we will discuss it more precisely.

If L-502 is used at the highest possible data acquisition frequency from each channel, then set  $\mathbf{n}_{sw} = 1$ , which means that the sampling period of one measurement channel is  $\mathbf{t}_{sw} = \mathbf{t}_{ref}$ , during which only one ADC sample is converted. For example, for  $\mathbf{f}_{ref}=2$  MHz time $\mathbf{t}_{sw} = \mathbf{t}_{ref} = 0.5 \ \mu s$  is a fairly short switching period of the channel switch, which imposes restrictions on the output impedance of the signal source (and the wires from it): the impedance should be sufficiently small (not more than 50 Ohm) and not have a large reactive component, so that the duration of the transient process caused by circuit switching does not exceed 0.5  $\mu s$ . In other words, the signal source should be no more than 50 Ohm and have a short or coordinated cable. For those who used the L-783, these requirements and these conditions of use roughly correspond to the conditions of application of the L-783 in the multichannel mode with the maximum ADC conversion frequency of the 3 MHz, but with the difference that the L-502 ADC's resolution is 16 bits, not 12, and the electronic switch in L-502 is much more "quiet" (i.e. it injects a significantly smaller parasitic charge into the signal chain at the time of commutation, and therefore causes a significantly smaller shock excitation for a possible transient process in the signal circuit).

But if you want to use L-502 at a data acquisition rate for each channel less than the maximum, and you can reduce the switching frequency, then in L-502 with internal synchronization there is no reduction in the frequency of ADC startup, and  $\mathbf{n}_{sw} > 1$  is set, for example, as it is shown on fig. 3-1. But, in the sense of  $\mathbf{n}_{sw}$  – this is the number of cycles of ADC conversion for one

switching period. L-502 has, by default, that for  $\mathbf{n}_{sw} > 1$  all ADC readouts are flipped, except for the last one, during the switching period - this creates the greatest time for setting the signal after switching (due to "idle" ADC conversion cycles), therefore the least stringent requirements are imposed to the impedance of the signal source. On fig. 3-3, with  $\mathbf{n}_{sw} = 3$ , such conditions are set "by default" for the logical channel 1: the first two counts are always discarded, and the third one is used. But the real tasks of using multichannel ADCs do not assume that the impedances of the signal sources are the same, and for channels with connected low-impedance sources it would be good not to discard at least some of the ADC samples, but to use them for averaging the data, thereby increasing the enable when measuring this channel. This possibility is provided in L-502 due to the fact that in every cell of the control table, besides the physical channel number, there is also the averaging factor  $\mathbf{n}_{av}$ , by default,  $\mathbf{n}_{av} = 1$ . Averaging factor  $\mathbf{n}_{av} = \{1, 2, ..., 128\}$  means: "how many counts of the ADC from the end of the switching cycle of this channel will be used to averaging the data". Accordingly,  $\mathbf{n}_{su} = \mathbf{n}_{sw} - \mathbf{n}_{av}$  means "how many ADC counts from the beginning of the switching cycle of the given channel will be discarded", or "how many periods  $\mathbf{t}_{ref}$ will be used to set the signal at the ADC input after switching".

For example, on fig. 3-3 for navigational channel 2,  $\mathbf{n}_{av} = 2$  is installed in the control table, which means that for  $\mathbf{n}_{sw}=3$  the result of the last two conversion periods in one switching phase will be used for averaging, and one first period is added to the time of signal establishment after switching. For logical channel 3, all three samples of the ADC are used for averaging, and therefore the minimum time is assigned here to establish a signal after switching.

#### Fig. 3-3. The principle of obtaining ADC data (in detail)

From fig. 3-3 it also follows that the set non-zero interframe delay actually increases the settling time for the first logical channel. This can be used, for example, by associating the first logical channel with the physical channel to which the signal source is connected by the largest impedance.

It can be argued that by setting optimal  $n_{su} / n_{av}$  settings for each channel, we are trying to optimize the *timing of the signal conditioning* associated with the inter-channel passage and the *resolution of the ADC*.

It is important to note that in the L-502, the ADC averaging algorithm described here (by the simple average method) is considered as an inseparable part of the analog-to-digital converter itself, although physically the averaging procedure is performed by means of FPGA using 24-bit integer arithmetic.

Such an averaging operation increases the real resolution of the ADC by suppressing the random components of the signal of different nature, improves the signal/noise by suppressing the high-frequency components of the spectrum above the Nyquist frequency of  $0.5*f_{ch}$  for a given physical channel associated with one (or more) logical channel. Note in passing that digital filtering by the Blackfin processor (or high-level software) has a fundamentally different active filtering area, because it is below the Nyquist frequency.

Once again, we emphasize that "default" settings of L-502 have  $n_{av}=1$ , and there is no averaging process "by default".

#### 3.3.7. Relative switching delays in ADC channels.

This information will be important only for that class of multi-channel data acquisition tasks where the magnitude of the relative signal delay between the ADC channels is important for measuring relative phase delays. For this class of problems, the theoretical calculated latency values in the ADC channels are taken into account in the delay equalization algorithm based on one or another method of signal interpolation.

For ADC mode without averaging  $(n_{av}=1)$ , the relative switching delay between adjacent ADC channels within one frame (in the order of polling the control table) is equal to  $t_{sw}$ , and between the last channel of the previous frame and the first channel of the next one is  $t_{sw} + t_d$ .

If the averaging mode is used  $(n_{av}>1)$ , where  $n_{av}$  are selected equal for all ADC channels, the absolute delay for each channel will decrease by the same amount  $0.5*n_{av}*t_{ref}$ . Therefore, the relative delay will remain equal to  $t_{sw}$  between neighboring channels of one frame and equal  $t_{sw} + t_d$  between the nearest channels of neighboring frames separated by interframe delay.

If the averaging mode is used  $(\mathbf{n}_{av}>1)$ , where  $\mathbf{n}_{av}$  are assigned in the control table different for i- and j-th logical ADC channel, the absolute signal delay on the i- channel will decrease by  $0.5\mathbf{n}_{av}(i)*\mathbf{t}_{ref}$ , and the relative delay j channel towards the previous i- (within one frame) becomes  $\mathbf{t}_{sw} + 0.5* \mathbf{t}_{ref} (\mathbf{n}_{av}(i)-\mathbf{n}_{av}(j))$ , or becomes equal to  $\mathbf{t}_{sw} + \mathbf{t}_d + 0.5* \mathbf{t}_{ref} (\mathbf{n}_{av}(i)-\mathbf{n}_{av}(j))$  between the nearest i-th and next j-th channels of neighboring frames separated by interframe delay (if more precisely, for the last channel in the frame always i =  $\mathbf{n}_k$ , and for first, always j = 1).

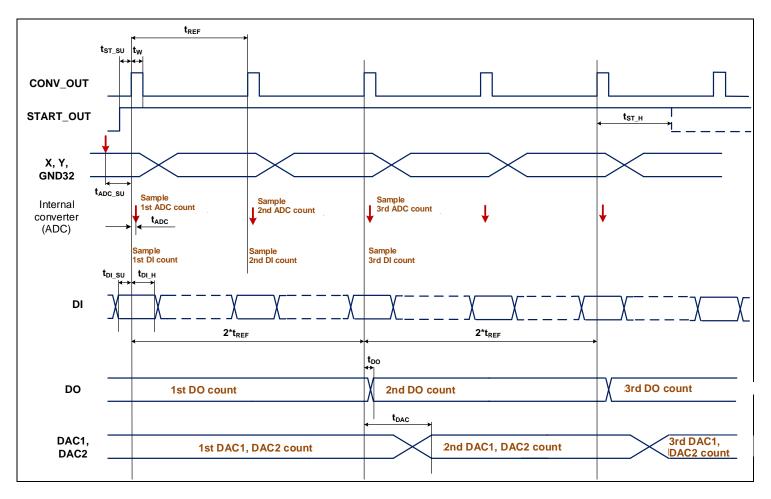

#### 3.3.8. Relative delays of the ADC, DAC and I/O channels.

Fig.3-4. Synchronous I/O diagram

In the above-mentioned synchronous I/O diagram, the output signal CONV\_OUT is used as a reference clock signal, with respect to which all I/O delays are described. Temporal parameters of the diagram are described in the table below. The delays in the ADC channel are given for the operating mode without averaging the data and without allocating additional cycles of the ADC for setting the signal

| Description                                                                 | Desig-              | Timing sample |                                    |         |

|-----------------------------------------------------------------------------|---------------------|---------------|------------------------------------|---------|

|                                                                             | nation              | Minimum       | Typical                            | Maximum |

| Reference frequency period                                                  | t <sub>REF</sub>    |               | 500 ns (2 MHz)<br>667 ns (1.5 MHz) |         |

| Duration of the signal pulse CONV_OUT                                       | tw                  |               | 50 ns                              |         |

| Group delay time of analog path of ADC channel in L-502                     | t <sub>ADC_SU</sub> |               | 15-70 ns                           |         |

| The delay time from the front CONV_OUT to the sampling time of the ADC chip | t <sub>ADC</sub>    |               | 0 ns                               |         |

| Description                                                                                              | Desig-             | Timing sample |         |         |

|----------------------------------------------------------------------------------------------------------|--------------------|---------------|---------|---------|

|                                                                                                          | nation             | Minimum       | Typical | Maximum |

| The time to set the state "1" to<br>START_OUT before the front<br>CONV_OUT<br>(start of data collection) | t <sub>ST_SU</sub> | 45 ns         |         |         |

| Hold time of state "1" to START_OUT<br>after the front CONV_OUT<br>(termination of data collection)      | t <sub>ST_H</sub>  | 150 ns        |         |         |

| The time to set the data at the DI input                                                                 | t <sub>DI_SU</sub> |               | 5 ns    |         |

| Data hold time at the DI input                                                                           | t <sub>DI_H</sub>  |               | -1 ns   |         |

| DO delay time relative to the front<br>CONV_OUT                                                          | t <sub>DO</sub>    |               | 6 ns    |         |

| The group delay time of the signal at the output of the DAC relative to the front CONV_OUT               | t <sub>DAC</sub>   |               | 0,7 μs  |         |

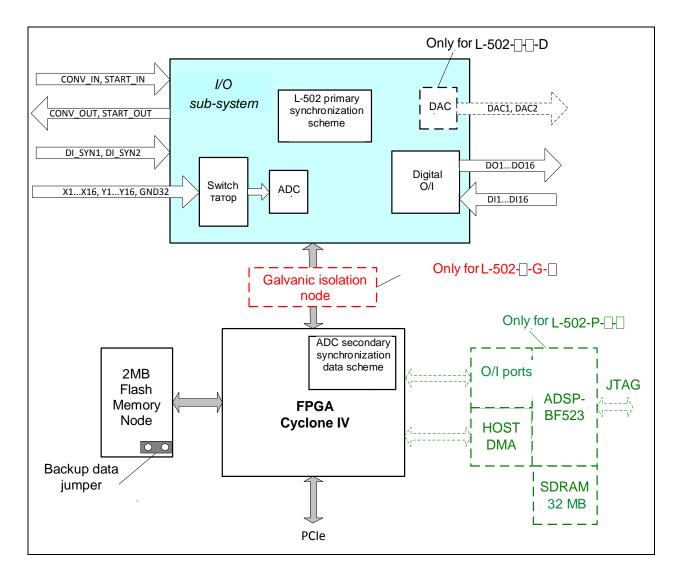

## 3.4. Operation principle and function circuit

Fig. 3-5. Block diagram

FPGA is the basic logical element in the L-502, in which all the interface functions, the hardware logic of ADC calibration, and the logic of the *secondary synchronization* are concentrated (3.3.5)

Flash-memory with a capacity of 2 MB is designed to store the main and backup firmware FPGA, calibration factors, serial number. Half the amount of Flash memory is provided for user tasks.

The L-502 I/O subsystem includes nodes for the channel switch, ADC, DAC (L-502---D), digital I/O, and *primary synchronization* circuit (3.3.5).

The galvanic isolation unit (L-502--G--G) isolates all circuits of the I/O subsystem from circuits connected electrically to any circuits of the computer.

The ADSP-BF523 signal processor (L-502-P-)) is designed for additional data processing and control. If the processor is enabled, the entire data stream and the I/O subsystem are transferred through the processor's I/O ports. For example, it is possible to create a control loop through a

signal processor. The interface of the processor with the computer is through the HOST port of the DMA processor.

The signal processor has 32 MB SDRAM (L-502-P-----).

When the computer's power is turned on, before the BIOS of the computer starts initializing the devices, the L-502 will download the firmware to the FPGA from Flash memory (fig. 3-5), and the L-502 internal power supply system will be fully turned on. In this case, the option of loading the main/backup firmware will depend on the status of the backup boot jumper (sec. 2.1.1).

After loading the FPGA, the L-502 becomes a PCI Express device, which will be assigned the appropriate system resources when the OS is initialized.

## Chapter 4. Connection of signals.

This chapter provides information on the L-502 connectors, the assignment of their contacts, and the main characteristics of the L-502 inputs and outputs related to the correct connection.

## 4.1. GND, DGND, AGND circuits.

L-502 has the following the following conventions for earth circuits (or "common wire" circuits for an interface):

GND is the ground circuit of the computer's system unit, electrically connected to the computer chassis, with the computer's mains plug ground, the GND circuit of the computer's motherboard, with the GND PCI Express circuit.

AGND is a "common wire" circuit of analog circuits: ADC inputs and DAC outputs.

DGND is a circuit of the "common wire" of digital circuits: digital inputs and outputs.

In any modification of the L-502, the AGND and DGND circuits have a common connection point inside the L-502

In L-502--X- (without galvanic isolation) the GND circuit has an internal connection point with DGND, which in turn is connected to AGND.

### 4.2. L-502 connectors description.

4.2.1. L-502 external signal connector.

The external signal connector is a 37-pin 2-row type DRB-37M plug that extends outward when the L-502 module is installed inside the PC unit. The bracket L-502 is directly fixed to the DRB-37M connector with 6-point screws.

The conductive contact of the connector (screen) is always electrically connected to the computer case (GND circuit).

#### 4.2.2. Connecting the cable shield.

On the casing of the cable part of the DB-37F signal connector it is possible to directly seal the screen of the signal cable for any modification of the L-502, however, as shown by the L-502 practice, **the best signal-to-noise ratio is obtained by connecting the cable shield to the AGND signal connector** (there are no connections to the connector housing).

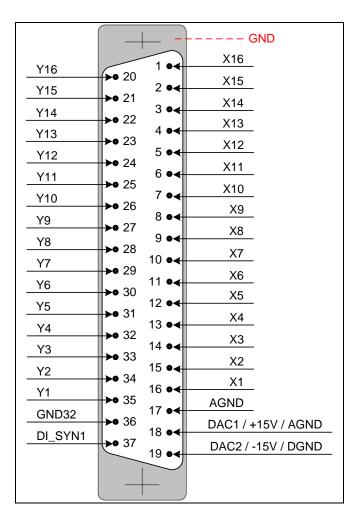

Fig. 4-1: Eternal signal connector

Table 4-1: Eternal signal connector

| Signal name | Comm<br>on<br>point <sup>5</sup> | Direc-<br>tion | Description                                                                                                                                     |

|-------------|----------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| X<116>      | AGND                             | Input          | • Non-inverting channel voltage input 1 16 for differential and "common ground" mode:                                                           |

|             |                                  |                | • Operation voltage range: ±10 V (see the details in section 4.4 p. 44).                                                                        |

|             |                                  |                | • Unused inputs X <1 16> are recommended to be connected to AGND or the corresponding physical channel not to be interrogated programmatically. |

| Y<116>      | AGND                             | Input          | • Inverting channel voltage input 1 16 for differential mode.                                                                                   |